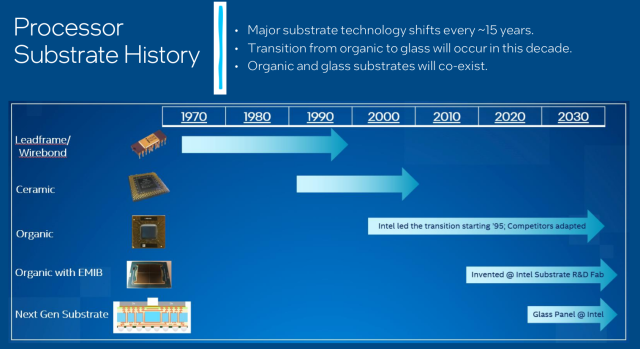

인텔이 차세대 반도체 제조에 활용하기 위해 투자하고 있는 유리 기판(glass substrate) 패키징 기술을 공개했다. 오는 2030년까지 이 기술을 상용화해 고성능 인공지능(AI)·데이터를 다루는 고성능 서버 시스템용 칩을 만드는 데 우선 적용할 예정이다.

19일 인텔은 지난 10년 이상 유기 기판을 대신할 유리 기판의 신뢰성을 연구·검증해 왔으며 이르면 2025년, 늦어도 2030년까지 완전한 유리 기판 솔루션을 시장에 선보일 계획이라고 밝혔다. 유리 기판 기술은 반도체 패키지 내 트랜지스터 확장과 데이터 중심 애플리케이션을 제공하기 위한 무어의 법칙을 지속할 수 있게 할 핵심 기법이라고 강조했다.

인텔은 유리 기판이 고온 내구성을 갖고 있고 패턴 왜곡 발생률이 50% 낮으며 웨이퍼 리소그래피 초점 심도를 개선하는 평탄도(ultra low flatness)와 촘촘한 레이어 간 인터커넥트 오버레이에 필요한 구조 안정성을 갖췄다고 강조했다. 유리 기판을 적용하면 인터커넥트 밀도를 10배 높일 수 있고 높은 조립 수율로 초대형 폼팩터 패키지를 구현할 수 있다고 주장했다. 유리 기판을 적용해 제조한 칩은 데이터센터, AI, 그래픽 등 고성능 애플리케이션과 워크로드를 빠르게 처리해야 하는 산업 영역에서 우선 쓰일 것이라고 인텔은 전망했다.

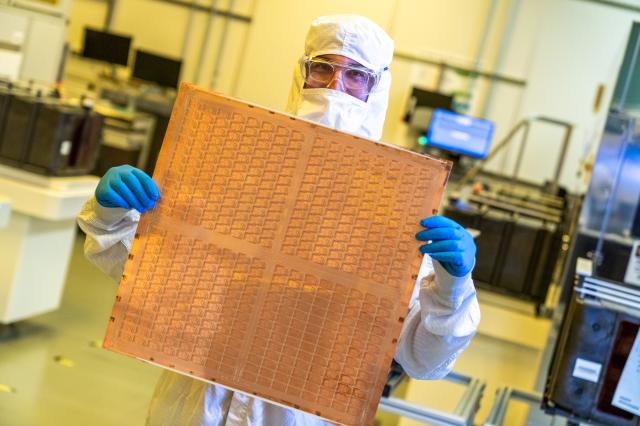

인텔은 2021년부터 시작한 ‘인텔파운드리서비스(IFS)’ 사업에도 이번 유리 기판 패키징 기술을 투입할 계획이다. 미국 애리조나주 챈들러 지역의 ‘조립 및 테스트 기술 개발 공장’에서 유리 기판과 같은 차세대 반도체 제조에 활용하기 위한 첨단 패키징 기술을 연구·검증하고 있다. 첨단 반도체 패키징 영역에서 삼성전자·TSMC와 기술 선도 경쟁을 지속하기 위해 투자를 지속해 나갈 전망이다.

바박 사비(Babak Sabi) 인텔 조립 및 테스트 기술 개발 부문 총괄 부사장은 “10년간의 연구 끝에 인텔은 첨단 패키징에 활용할 업계 선도적인 유리 기판을 확보했다”며 “앞으로 수십년간 주요 업체 및 파운드리 고객이 수혜를 누릴 수 있는 최첨단 기술을 선보일 것으로 기대한다”고 말했다.

![[포토] 서울 시청역 교차로서 대형 교통사고](https://image.ajunews.com/content/image/2024/07/01/20240701224349454490_518_323.jpg)

![[포토] 한·베트남 비즈니스 포럼](https://image.ajunews.com/content/image/2024/07/01/20240701162227446930_518_323.jpg)

![[포토] 여의도공원 상공에 뜬 서울달](https://image.ajunews.com/content/image/2024/06/28/20240628150225695491_518_323.jpg)

![[포토] SK바이오사이언스, 독일 백신위탁생산 기업 인수 관련 기자간담회](https://image.ajunews.com/content/image/2024/06/27/20240627111510278341_518_323.jpg)

![[금투세 폐지 논란] 코리아 디스카운트 심화...韓증시 불확실성 높여](https://image.ajunews.com/content/image/2024/01/03/20240103150426112900_388_136.jpg)