[삼성전자 제공]

또한 그동안 대규모 투자를 통해 삼성 따라잡기에 나선 중국 업체들의 추격도 따돌릴 수 있는 계기가 마련됐다.

시장이 공급과잉인 상황에서 삼성전자는 시장점유율을 넓히고 양산 수율을 경쟁사 대비 월등한 수준으로 높이며 홀로 승승장구하고 있다.

메모리 반도체 낸드플래시 시장에서는 이미 삼성전자가 3D낸드를 단독 양산하며 메이저 중에서도 2년 이상의 기술 격차를 벌린 상태다.

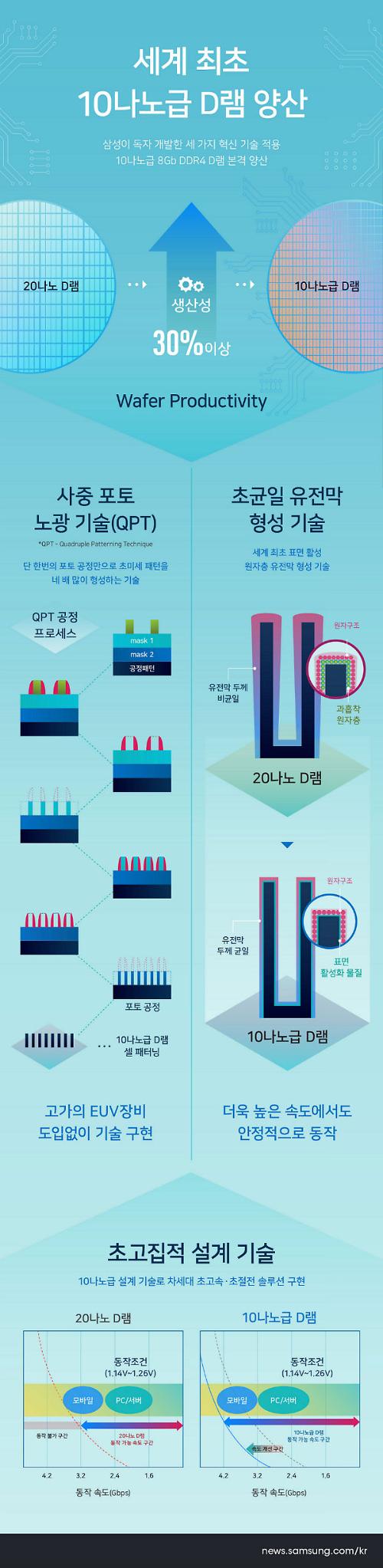

삼성전자는 D램 10나노대 진입을 위해 '초고집적 설계 기술'과 '사중 포토 노광 기술(Quadruple Patterning Technique)', '초균일 유전막 형성 기술' 등 3가지 혁신 기술을 개발했다. 이에 따라 차세대 극자외선(EUV) 노광장비의 도입 없이도 10나노급 D램을 양산해 프리미엄 제품의 제조 경쟁력을 더욱 높일 수 있게 됐다.

초고집적 설계 기술은 삼성전자가 독자적으로 개발한 차세대 반도체 설계 기술로, 이를 통해 20나노 8Gb(기가비트) DDR4(Double Data Rate 4) D램보다 생산성을 30% 이상 높였다.

또한 10나노급(1x) 8Gb DDR4 D램은 기존 20나노 대비 동작속도가 30% 이상 빠른 3200Mbps를 구현할 수 있고, 동작 상태에 따라 소비전력을 10%~20% 절감할 수 있어 차세대 엔터프라이즈 서버 시장에 최적의 솔루션을 제공할 것이라고 회사측은 설명했다.

삼성전자는 미세공정의 한계를 극복하기 위해 낸드플래시 양산에 적용한 '사중 포토 노광 기술'을 업계 최초로 D램에도 구현해 D램 핵심 공정 기술의 새로운 지평을 열었다. 이 기술은 초고집적으로 셀을 만들기 위해 한번의 포토공정으로 초미세 패턴을 4배 많이 형성하는 기술이다.

셀(정보 저장의 최소 단위)이 트랜지스터 하나로 구성된 낸드플래시와 달리 D램은 트랜지스터와 캐패시터의 적층 구조로 셀이 구성된다. 이 때문에 10나노급 8Gb D램은 초고속으로 동작하는 트랜지스터 위에 고용량 캐패시터를 나노단위 간격으로 배열해 완벽하게 동작하는 셀을 80억개 이상 만들어야 하므로 미세화에 따른 개발 난이도가 높았다. 삼성전자는 이러한 D램의 공정 한계를 사중 포토 노광 기술을 통해 극복해 차세대 10나노급(1y) D램도 적기에 양산할 수 있는 기반 기술을 확보했다.

D램은 초미세 캐패시터에 충분한 양의 전하를 저장하기 위해 초균일 원자 유전막 형성 기술이 필요하다. 이번 10나노급 D램은 캐패시터의 유전막을 옹스트롬(10분의 1나노) 단위의 초박형 원자 물질로 균일하게 형성해 더욱 높은 속도에도 안정적으로 동작하는 우수한 셀 특성을 확보했다.

한편 삼성전자는 지난해 4분기 D램 시장 점유율 46.4%를 기록해 압도적인 시장 지배력을 나타냈다. 작년 3분기에는 46.7%로 역대 최고치를 찍었다.

낸드플래시 시장에서도 지난해 4분기 40.2%를 기록해 3년 반 만에 다시 40%를 돌파했다.

![[2024 서민금융포럼] 이복현 금감원장 서민금융 위한 포괄적 선택지 모색해야](https://image.ajunews.com/content/image/2024/11/21/20241121133047477780_388_136.jpg)

![[포토] 제8회 서민금융포럼](https://image.ajunews.com/content/image/2024/11/21/20241121114536531007_518_323.jpg)

![[포토] 기조연설 하는 페이커 이상혁](https://image.ajunews.com/content/image/2024/11/20/20241120115246771576_518_323.jpg)

![[포토] 발왕산은 벌써 겨울](https://image.ajunews.com/content/image/2024/11/19/20241119205226273772_518_323.jpg)

![[슬라이드 포토] 제44회 황금촬영상 시상식 참석한 스타들](https://image.ajunews.com/content/image/2024/11/18/20241118194949259743_518_323.jpg)